Le PCI Express 6.0 est déjà en préparation pour 2021 (maj)

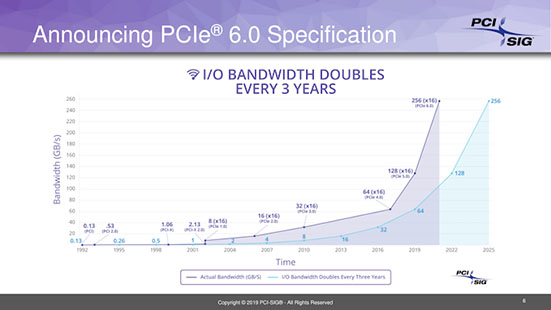

On le sait bien, l’évolution va toujours très vite en informatique mais là on atteint tout de même des sommets ! La norme PCI Express 4.0 commence seulement à arriver, les produits ne sont même pas encore disponibles en magasins, que déjà on parle du PCI Express 5.0 pour l’année prochaine et maintenant il est même question du PCI Express 6.0 pour 2021.

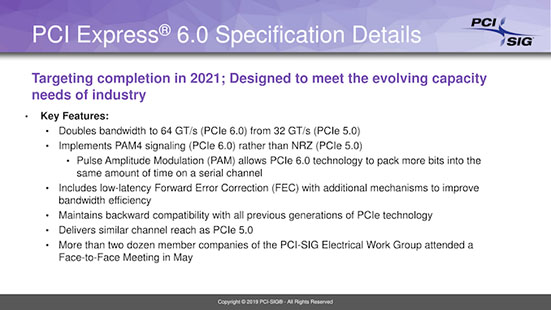

La sixième génération de la norme PCI Express permettra une nouvelle fois de doubler les débits de la norme précédente, ce qui correspond à 64 GT/s en PCI Express 6.0 contre 32 GT/s pour le PCI Express 5.0 (qui n’est pas encore dispo rappelons le). Concrètement il sera donc possible d’atteindre un débit de 256 Go/s sur 16 lignes PCI Express.

La bonne nouvelle c’est que la norme PCI Express 6.0 sera rétro compatible avec toutes les générations précédentes ce qui nous permettra de continuer à utiliser notre matériel actuel, qu’il s’agisse de cartes graphiques ou de SSD NVMe.

(Actualité publiée initialement le 19 juin 2019)

MAJ le 24 février 2020 : Les spécifications de la norme PCI Express 6.0 continuent leur petit bonhomme de chemin… Le consortium PCI-SIG annonce que la version 0.5 du PCI Express 6.0 a été ratifiée. C’est une nouvelle étape qui vient d’être franchie. Ca signifie que la norme PCI Express 6.0 est en bonne voie mais il va falloir patienter encore un peu pour qu’elle soit finalisée…

En effet, comme on peut le voir ci-dessous, le PCI-SIG doit encore dévoiler les versions 0.7 et 0.9 de la norme avant de passer à la version 1.0 qui correspondra à la version finale. C’est à partir de ce moment que nous pourrons trouver les premières cartes mères et les premiers produits exploitant les caractéristiques et les fonctionnalités du PCI Express 6.0. Si tout se passe comme prévu le PCI Express 6.0 devrait pointer le bout de son nez en 2021, c’est à dire l’année prochaine.

– Version 0.3 is beheld as a Concept and outlines the key features and architecture of the technology. In case of PCIe 6.0, we are talking about 64 GT/s per lane speed, pulse amplitude modulation with 4 levels (PAM-4) encoding, and forward error correction (FEC).

– Version 0.5 is considered as the First Draft specification and so it covers all the key aspects of the architecture and includes feedback from interested parties (within PCI-SIG) to version 0.3. Members of the group will be able to add new functionality to the technology at this point.

– Version 0.7 is deemed to be the Complete Draft, everything has to be defined at all levels and electrical specifications must have been validated via test chips. No new features may be added after release of this iteration of the specification.

– Version 0.9 is the Final Draft that is meant to allow PCI-SIG members to review the technology for their intellectual property.

– Version 1.0 is the Final Release.

Désolé, les commentaires sont fermés.